-

14 2022-07什么是等离子清洗机?

等离子清洗机(plasma cleaner)也叫等离子表面处理仪,是一种全新的高科技技术,利用等离子体来达到常规清洗方法无法达到的效果。对气体施加足够的能量使之离化便成为等离子状态。等离子体的“活性”组分包括:离子、电子、活性基团、激发态的核素(亚稳态)、光子等。等离子清洗机就是通过利用这些活性组分的性质来处理样品表面,从而实现清洁、改性、涂覆、光刻胶灰化等目的。

等离子清洗机,大部分人可能会感觉很陌生。事实上,等离子清洗机通过对样品表面进行改性(亲水性),同时除掉表面有机物,使多种材料之间能够进行贴合、涂覆、镀膜等工艺操作。从研究开发到工艺生产使用,从表面微细加工到表面处理改质效果都非常好,应用广泛。

等离子清洗机的原理是什么?

等离子体是物质的一种存在状态,通常物质以固态、液态、气态三种状态存在,但在一些特殊的情况下有第四种状态存在,如地球大气中电离层中的物质。等离子体状态中存在下列物质:处于高速运动状态的电子;处于激活状态的中性原子、分子、原子团(自由基);离子化的原子、分子;未反应的分子、原子等,但物质在总体上仍保持电中性状态。

等离子清洗机的优点:

一次超精密的清洗处理可以解决工件表面的附着力问题

可以去除肉眼看不见的有机污染物和表面吸附层,以及工件表面的薄膜层。一次超精密的清洗处理可以解决工件表面的附着力问题。低温等离子处理仅涉及材料的表面,不会对材料主体的性质产生影响。由于等离子体清洗是在高真空下进行的,所以等离子体中的各种活性离子的自由程很长,他们的穿透和渗透力很强,可以进行复杂结构的处理,包括细管和盲孔。

引入官能基团

等离子清洗在工件表面产生理想结合面,对聚合物和原材料进行上胶、印刷、焊接和喷涂等前处理。完全惰性的基材变成官能团材料,可以提高表面活性和浸润性,极大地提高了其使用价值。

可提升表面喷涂性能

应用等离子技术,可增强喷涂和表面处理的效果,这种聚合层可以达到非常致密,并且和基材结合的非常结实。

以上是常见的问题,如果有疑问或技术交流可以联系我们:13510685447,感谢关注!

-

22 2022-06等离子清洗在LED 封装工艺中的应用

近年来,由于半导体光电子技术的进步,LED的发光效率迅速提高,预示着一个新光源时代即将到来。目前,国产商品化白光发光二极管的发光效率已经达到100 lm/W,远远超过了15 lm/W 的白炽灯和60 lm/W 的荧光灯。日本企业已经开始量产162 lm/W 以上的白光发光二极管,这一指标超过了光效140 lm/W 的钠灯,就发光二极管的技术潜力和发展趋势来看,其发光效率将达到400lm/W 以上,远远超过当前光效最高的高强度气体放电灯,成为世界上最亮的光源。因此,业界认为,半导体照明将创造照明产业的第四次革命。

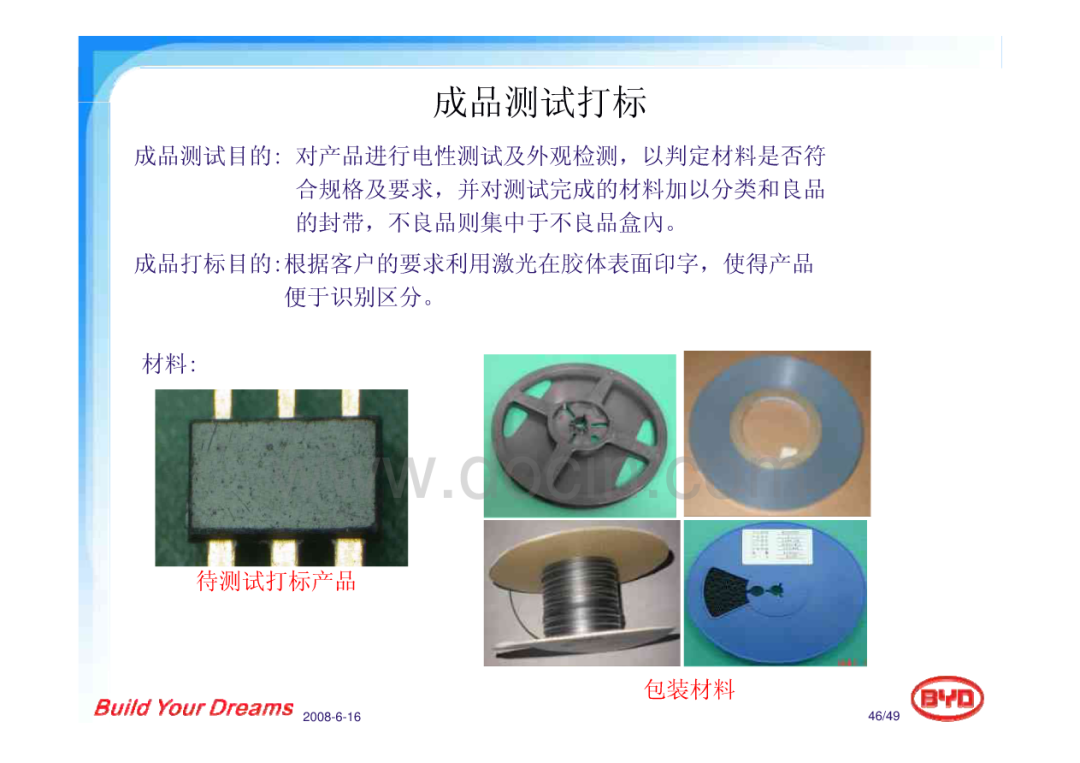

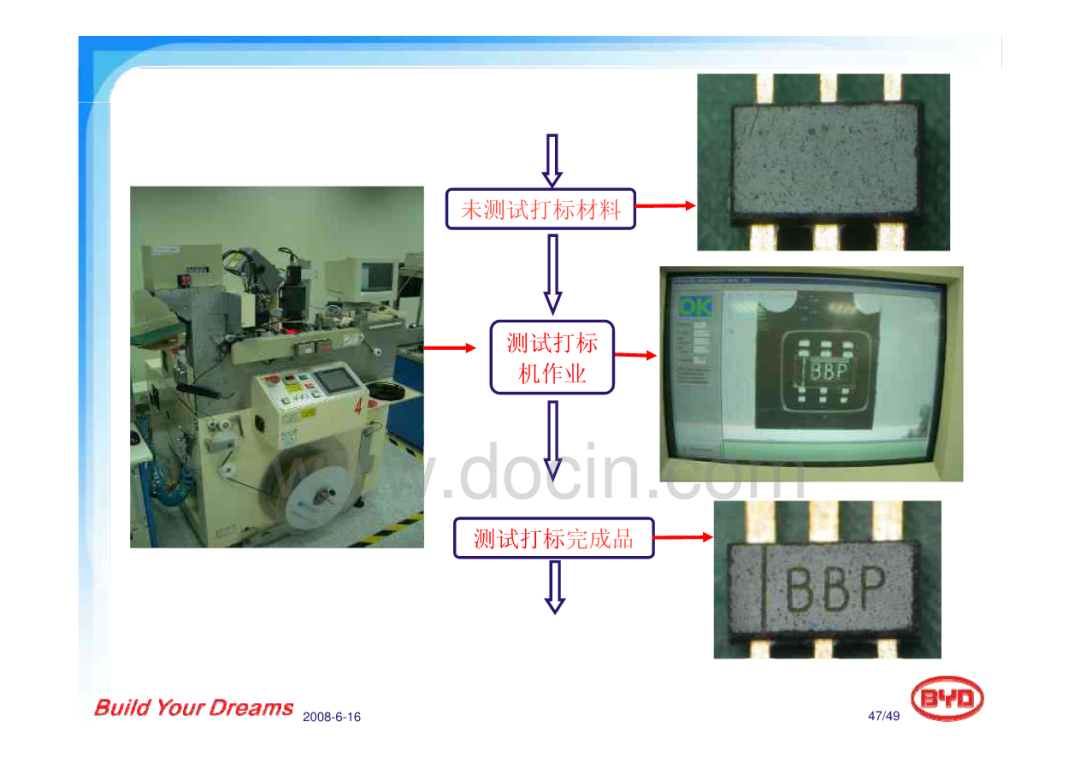

1 LED 的主要封装工艺

(1)芯片检验:材料表面是否有机械损伤及麻点麻坑;

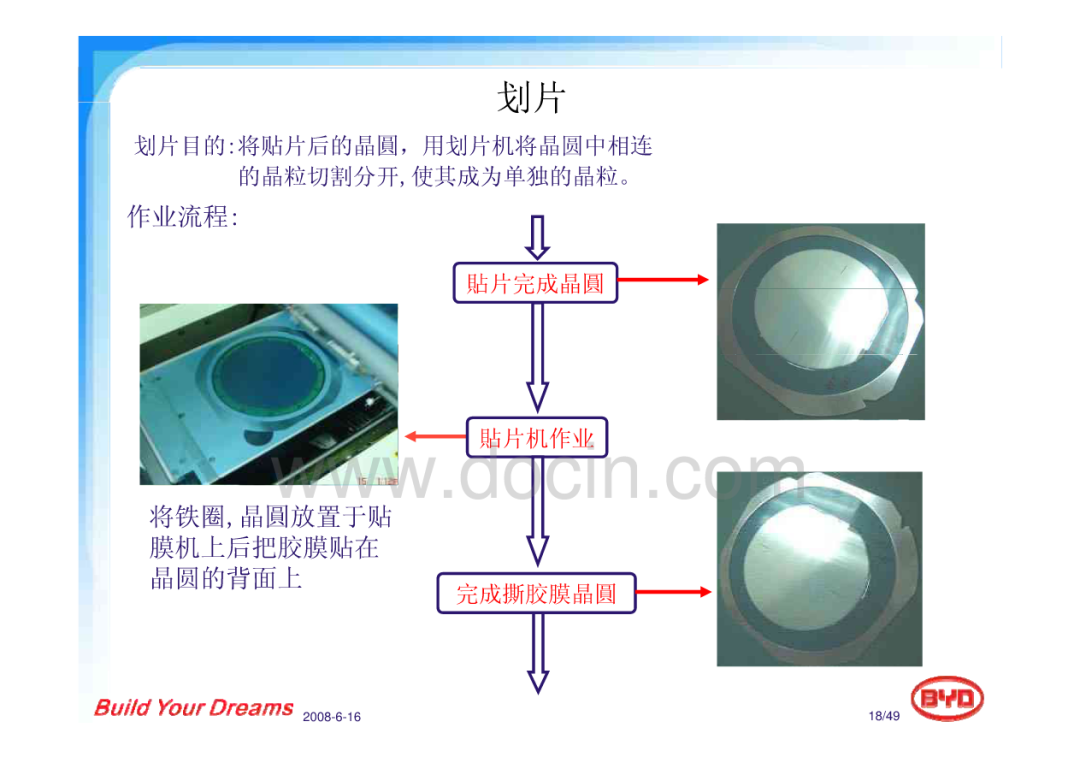

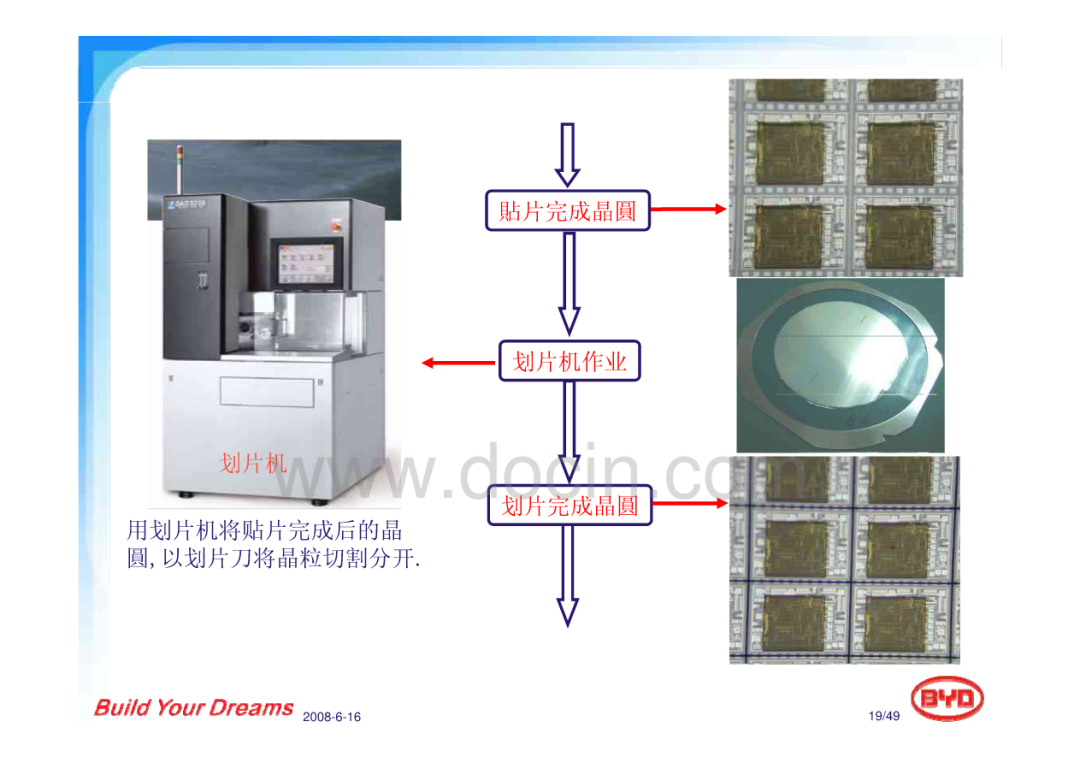

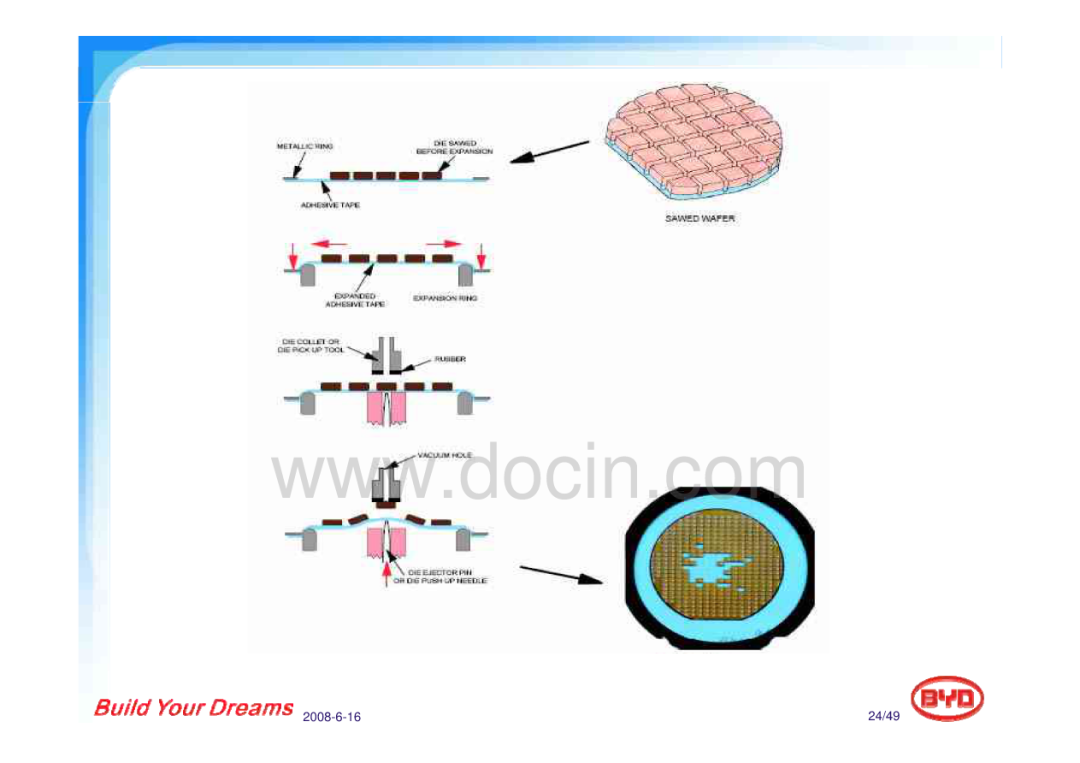

(2) LED 扩片:采用扩片机对黏结芯片的膜进行扩张,将划片后的LED 芯片由排列紧密约

0.1 mm 的间距拉伸至约0.6 mm,便于后工序的操作;

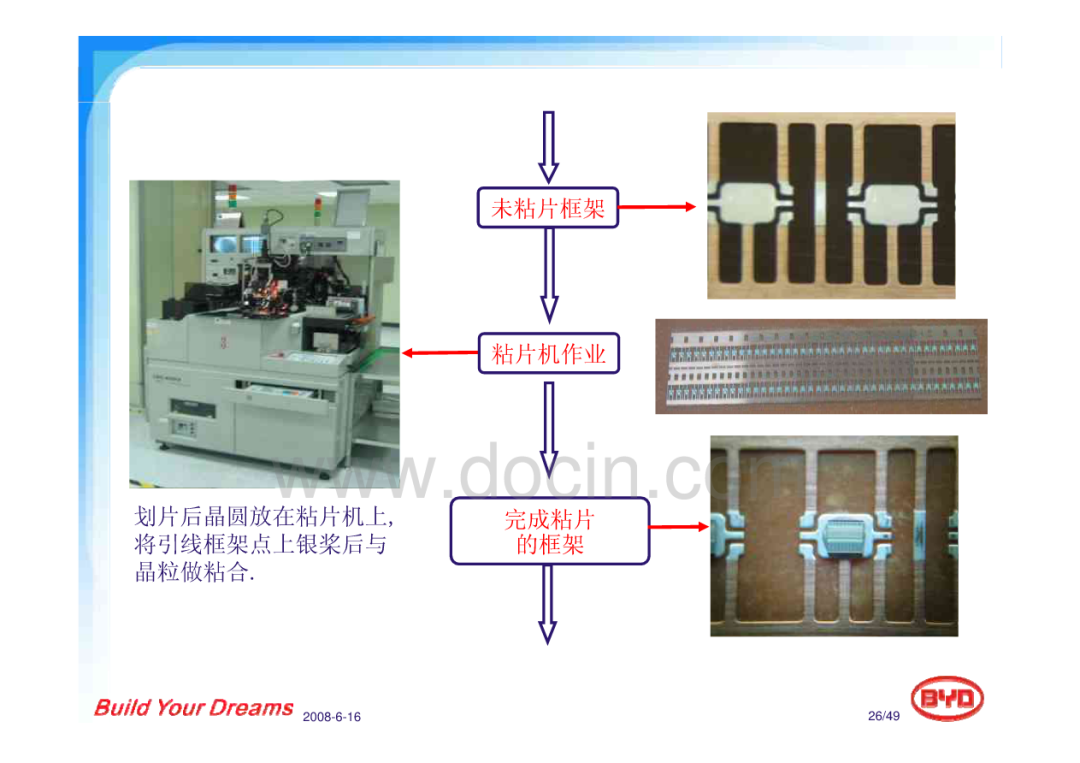

(3) 点胶:在LED 支架的相应位置点上银胶或绝缘胶;

(4) 手工刺片:将扩张后LED 芯片安置在刺片台的夹具上,并在显微镜下用针将LED 芯片一个一个刺到相应的位置上;

(5) 自动装架:自动装架结合了点胶和安装芯片两大步骤,先在LED 支架上点上银胶(绝缘

胶),然后用真空吸嘴将LED 芯片吸起移动位置,再安置在相应的支架位置上;

(6) LED 烧结:烧结的目的是使银胶固化,烧结要求对温度进行监控,防止批次性不良;

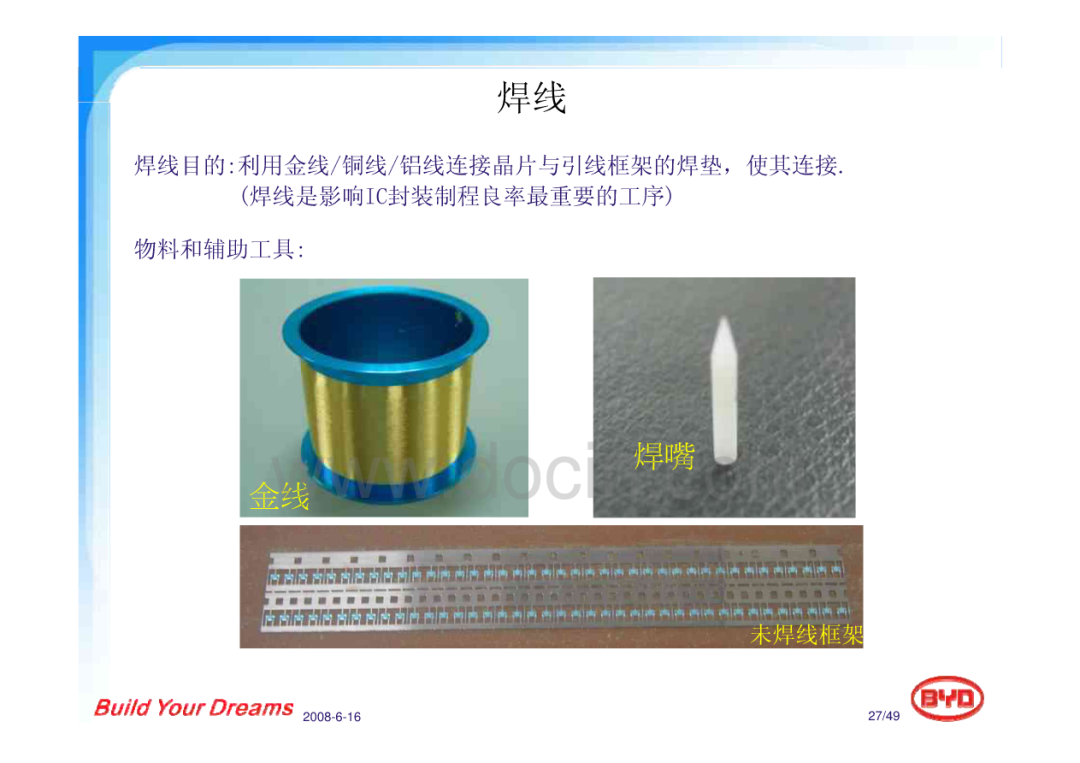

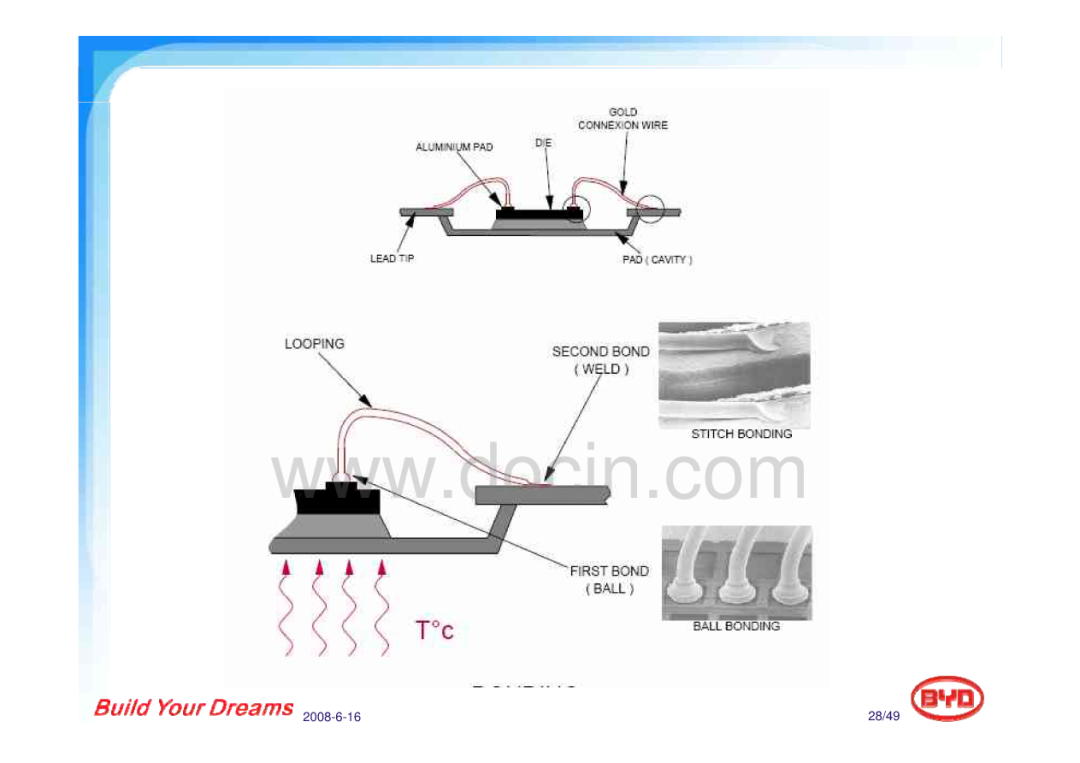

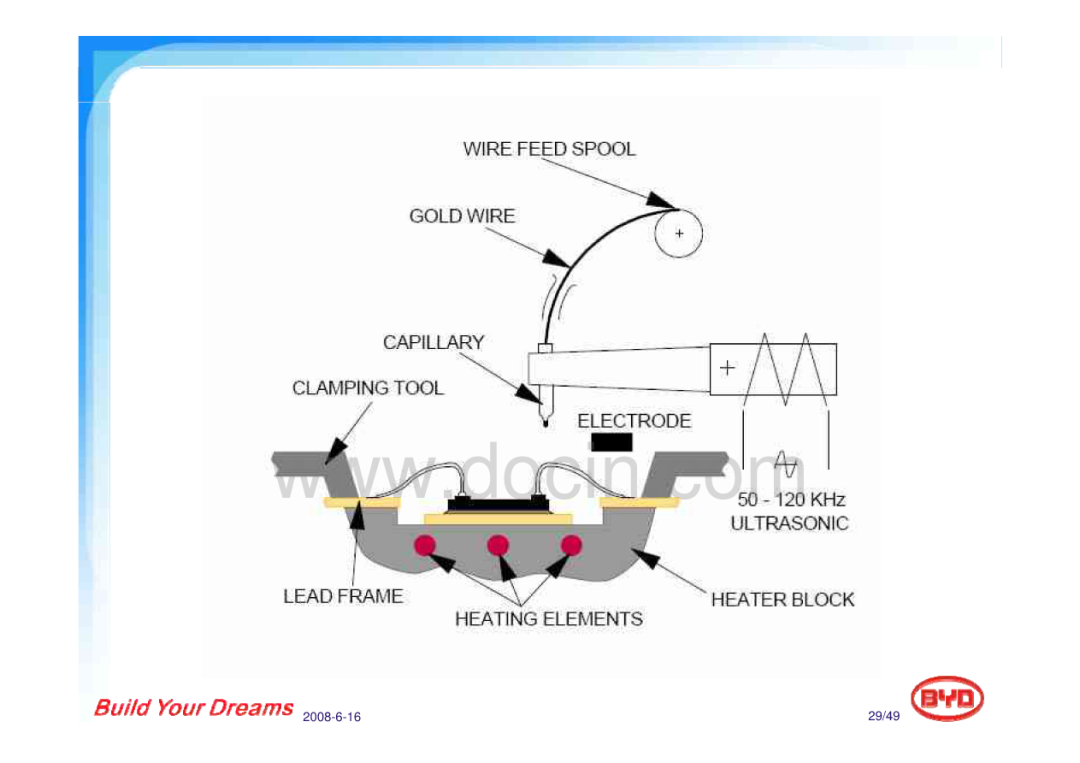

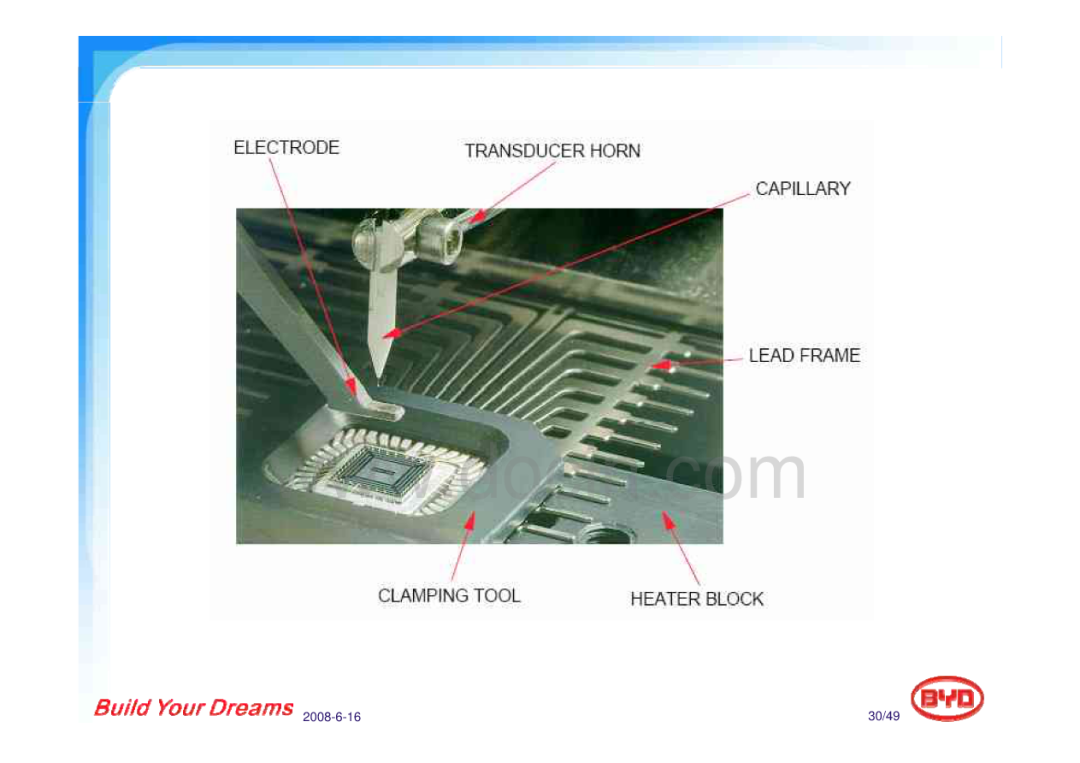

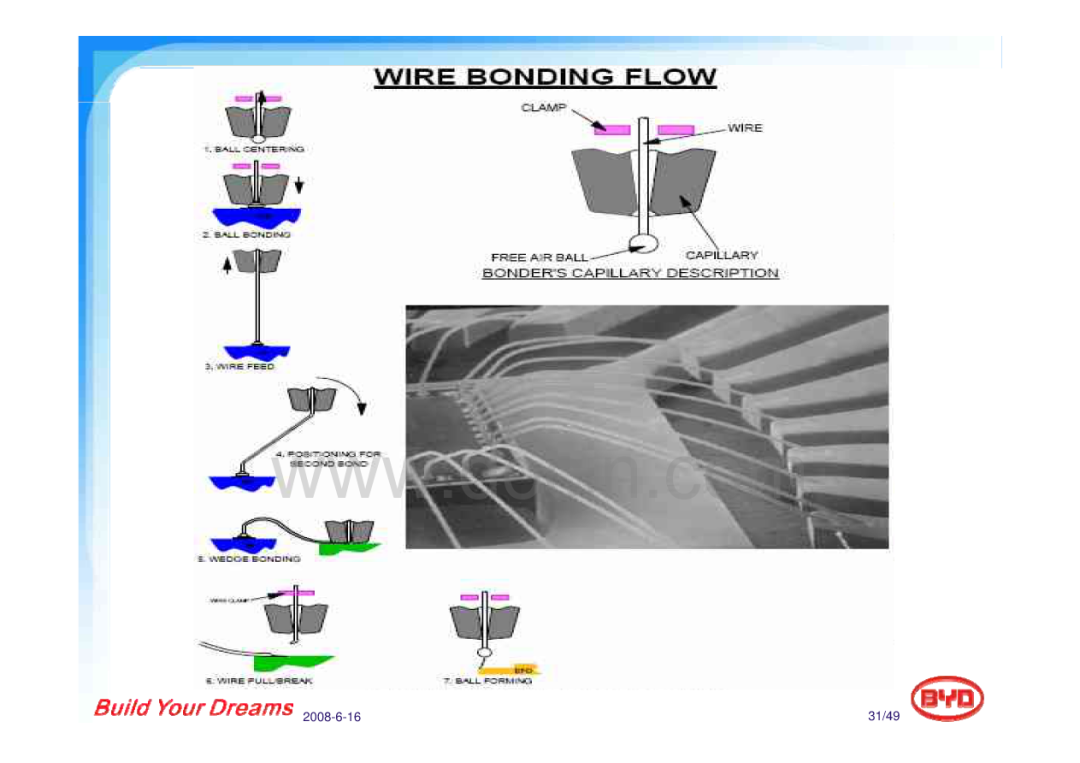

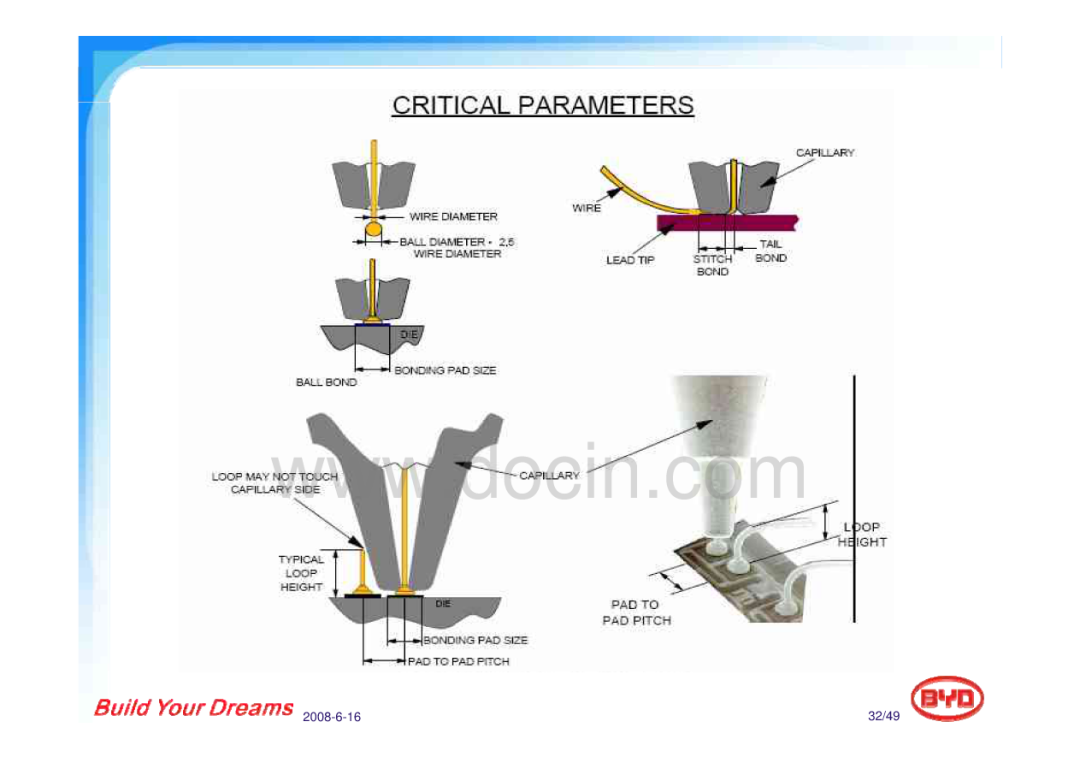

(7) LED 压焊:压焊是将电极引到LED 芯片上,完成产品内外引线的连接工作,LED 的压焊

工艺有金丝球焊和铝丝压焊两种;

(8) LED 封胶:LED 的封装主要有点胶、灌封、模压三种,基本上工艺控制的难点是气泡、多缺料、黑点,设计上主要是对材料的选型,选用结合良好的环氧和支架;

(9) LED 固化及后固化:固化即封装环氧的固化,后固化是为了让环氧充分固化,同时对LED进行热老化,后固化对于提高环氧与支架(PCB)的粘接强度非常重要;

(10) 切筋划片:由于LED 在生产中是连在一起的(不是单个),Lamp 封装LED 采用切筋切断LED 支架的连筋,SMD-LED 则是在一片PCB 板上,需要划片机来完成分离工作;

(11) 测试包装:测试LED 的光电参数、检验外形尺寸,同时根据客户要求对LED 产品进行分选,将成品进行计数包装,超高亮LED 需要防静电包装。

LED 制作过程中主要存在的问题:

(1) LED 制作过程中的主要问题难以去除污染物和氧化层。

(2) 支架与胶体结合不够紧密有微小缝隙,时间存放久了之后空气进入至使电极及支架表面氧化造成死灯。

解决方法:

(1)点银胶前。基板上的污染物会导致银胶呈圆球状,不利于芯片粘贴,而且容易造成芯片手工刺片时损伤,使用射频等离子清洗可以使工件表面粗糙度及亲水性大大提高,有利于银胶平铺及芯片粘贴,同时可大大节省银胶的使用量,降低成本。

(2)引线键合前。芯片粘贴到基板上后,经过高温固化,其上存在的污染物可能包含有微颗粒及氧化物等,这些污染物从物理和化学反应使引线与芯片及基板之间焊接不完全或粘附性差,造成键合强度不够。在引线键合前进行射频等离子清洗,会显著提高其表面活性,从而提高键合强度及键合引线的拉力均匀性。键合刀头的压力可以较低(有污染物时,键合头要穿透污染物,需要较大的压力),有些情况下,键合的温度也可以降低,因而提高产量,降低成本。

(3)LED 封胶前。在LED 注环氧树脂胶过程中,污染物会导致气泡的成泡率偏高,从而导致产品质量及使用寿命低下,所以,避免封胶过程中形成气泡同样是人们关注的问题。通过射频等离子清洗后,芯片与基板会更加紧密地和胶体相结合,气泡的形成将大大减少,同时也将显著提高散热率及光的出射率。

2 等离子体清洗机理

通常情况下,人们普遍认为的物质有三态:固态、液态、气态。区分这3 种状态是靠物质中所含能量的多少。气态是物质3 个状态中最高的能量状态。

其清洗原理是通过化学或物理作用对工件表面进行处理,实现分子水平的污染物去除(一般厚度为3~30 nm),从而提高工件表面活性。被清除的污染物可能有有机物、环氧树脂、光刻胶、氧化物、微颗粒污染物等,所以射频等离子清洗是一种高精密清洗。

就反应机理来看,等离子体清洗通常包括以下过程:

(1) 无机气体被激发到等离子态;

(2) 气相物质被吸附在固体表面;

(3) 被吸附基团与固体表面分子反应生成产物分子;

(4) 产物分子解析形成气相;

(5) 反应残余物脱离表面。

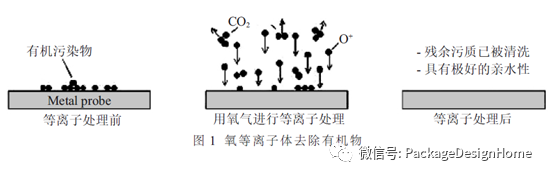

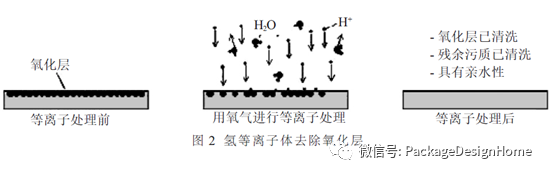

通过以下几个反应式及图1、图2 和图3 对清洗方式做详细说明。

2.1 化学清洗

表面反应以化学反应为主的等离子体清洗。

例1:

O2+e-→ 2O※ +e-

O※+有机物→CO2+H2O

从反应式可见,氧等离子体通过化学反应可使非挥发性有机物变成易挥发的H2O 和CO2。

例2:

H2+e-→2H※+e-

H※+ 非挥发性金属氧化物→金属+H2O

从反应式可见,氢等离子体通过化学反应可以去除金属表面氧化层,清洁金属表面。

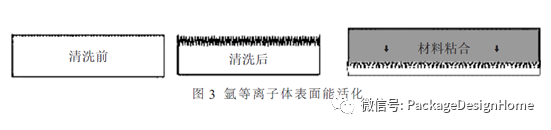

2.2 物理清洗

表面反应以物理反应为主的等离子体清洗。

例:

Ar+e-→Ar++2e-

Ar++ 沾污→挥发性沾污

Ar+ 在自偏压或外加偏压作用下被加速产生动能,然后轰击放在负电极上的被清洗工件表面,

一般用于去除氧化物、环氧树脂溢出或是微颗粒污染物,同时进行表面能活化。

物理化学清洗:表面反应中物理反应与化学反应均起重要作用。

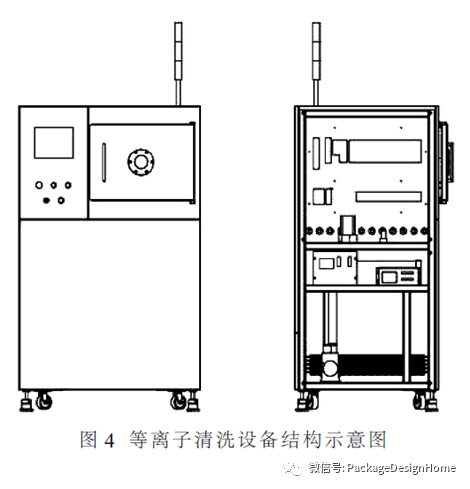

3 等离子清洗设备简介

射频等离子清洗设备的原理是先产生真空,在真空状态下,压力越来越小,分子间间距越来越大,分子间力越来越小,利用射频源产生的高压交变电场将氧、氩、氢等工艺气体震荡成具有高反应活性或高能量的离子,然后与有机污染物及微颗粒污染物反应或碰撞形成挥发性物质,然后由工作气体流及真空泵将这些挥发性物质清除出去,从而达到表面清洁活化的目的。

射频等离子清洗设备结构见图4。其结构主要由六部分组成:反应腔室、电控系统、供气系统、射频电源、真空系统、操作控制系统。

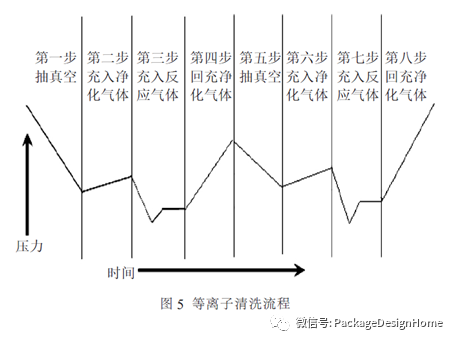

清洗流程如图5 所示。

4 清洗效果对比

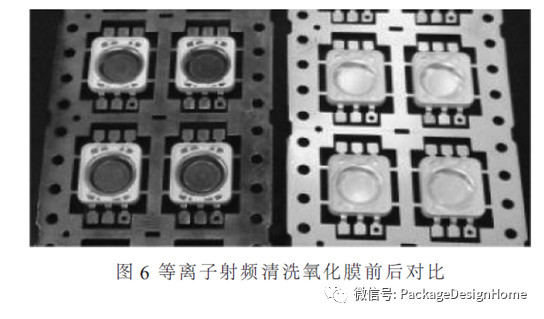

对某几家LED 厂家产品封装工艺前添加射频等离子清洗,测量键合引线的拉力强度,与未

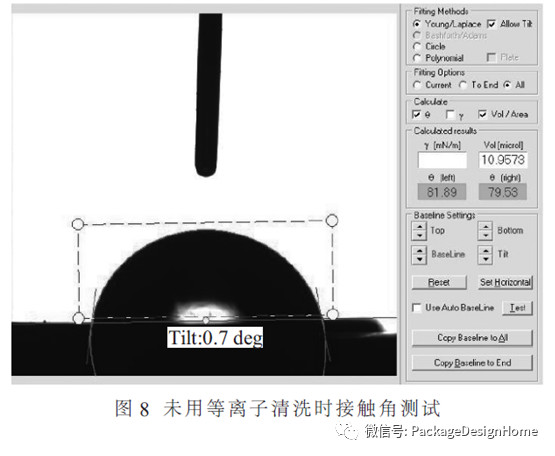

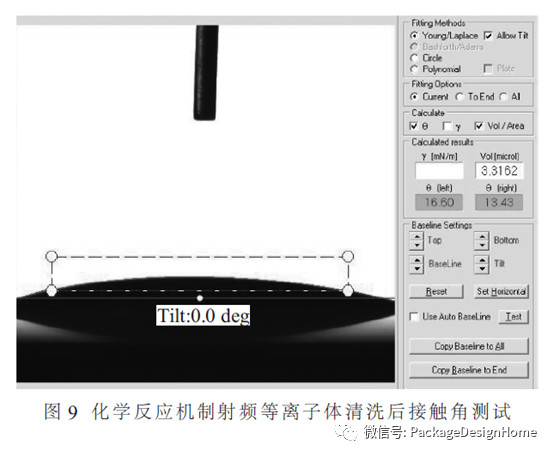

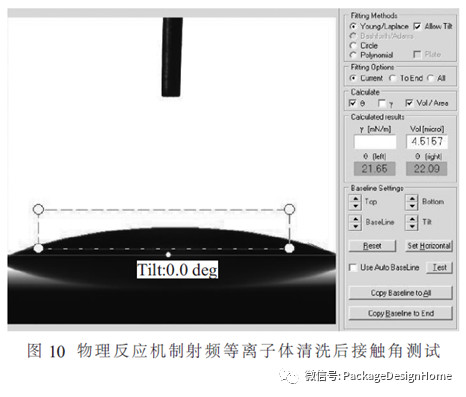

进行射频等离子清洗相比,键合引线拉力强度有明显增加(见图6、图7),反映基板及芯片进行射频等离子清洗后是否有清洗效果的另一个检测指标为其表面的浸润特性,通过对几家产品进行实验检测表明未进行过射频等离子清洗的样品接触角为70°~85°,如8 图;表面进行过化学反应机制射频等离子体清洗的样品接触角为10°~17°,如图9;而表面进行过物理反应机制射频等离子体清洗过的样品的接触角为20°~28°左右如图10。不同厂家、不同产品及不同清洗工艺的清洗效果是不同的,浸润特性的提高表明在封装工艺前进行射频等离子清洗是十分有益的。

5 结束语

射频等离子清洗是清洗方法中最为彻底的剥离式清洗,其最大优势在于清洗后无废液,最大特点是对金属、半导体、氧化物和大多数高分子材料等原基材料都能很好地处理,可实现整体和局部以及复杂结构的清洗。随着LED 产业的飞速发展,射频等离子清洗凭借其经济有效且无环境污染的特性必将推动LED 行业更加快速的发展.

本文章来源于网络,仅限于分享交流,如侵权请联络管理人员进行删除. -

07 2022-06四川大学博士生冯蕊《Nat. Commun.》:一种无掩模限域刻蚀的表面润湿性差异图案化新策略

近年来,四川大学化学学院环保型高分子材料国家地方联合工程实验室宋飞教授团队基于纤维素、大豆蛋白等生物质材料,制备了系列具有特殊润湿性(疏水-超亲水、疏水-超疏水、亲水-超亲水以及润滑-超亲水)的功能材料(Chem. Eng. J. 2021, 422, 130119.; Chem. Eng. J. 2021, 421, 127793.; Chem. Eng. J. 2020, 383, 123168; ACS Appl. Mater. Interfaces 2020, 12, 12373-12381; Chem. Eng. J. 2019, 369, 1040-1048; J. Colloid. Interf. Sci. 2019, 549, 123-132.; ACS Sustainable Chem. Eng. 2018, 6, 14679-14684; Chem. Eng. J. 2018, 352, 722-729.; Adv. Funct. Mater. 2018, 28, 1704956.)。但精确、复杂的图案化表面的制备往往需依赖光刻、等离子体刻蚀、飞秒激光等手段,限制了图案化润湿差异表面的发展与应用。

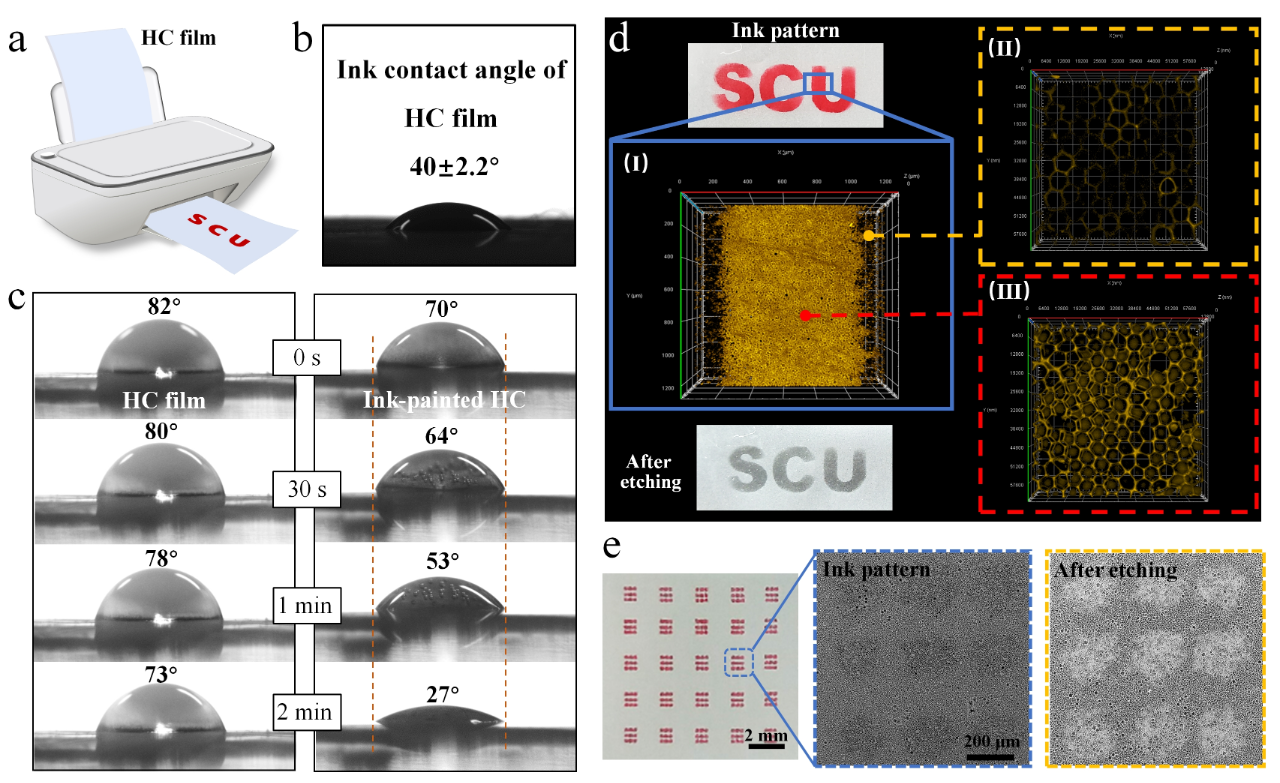

受可降解高分子材料分解过程因化学和物理结构改变导致材料表面润湿性变化所启发,四川大学化学学院环保型高分子材料国家地方联合工程实验室的博士研究生冯蕊近期提出了一种可控限域化学刻蚀策略,可实现精确、复杂图案化润湿差异表面的简单、快速制备。利用三醋酸纤维素在NaOH水溶液中的脱乙酰降解反应,结合水滴模板法与喷墨打印技术,在三醋酸纤维素多孔表面成功实现差异化碱刻蚀,从而制备了具有本征润湿差异的图案化表面。该方法操作简单易行、无需昂贵设备与耗材,可设计图案种类丰富且精度较高。表面图案区域与非图案区域具有明显润湿差异性,并且表面润湿性与微观形貌可通过控制脱乙酰化程度实现调控,在响应型信息存储与加密、柔性电子器件的制备等领域展现出良好的应用前景。

图1. 墨迹诱导碱水溶液差异化浸润实现图案化刻蚀

图2. 响应型信息存储与防伪应用

图3. 基于图案化表面的润湿差异实现柔性电极自铺展成形

该研究工作以“A Confined-Etching Strategy for Intrinsic Anisotropic Surface Wetting Patterning”为题发表于Nature Communications (Nat. Commun. 2022, 13, 3078),并已获授权发明专利ZL 202110570617.7。论文第一作者和通讯作者分别为博士研究生冯蕊和宋飞教授,该工作得到国家自然科学基金联合基金(重点项目,U21A2096)等项目的资助。

本文章来源于网络,仅限于分享交流,如侵权请联络管理人员进行删除. -

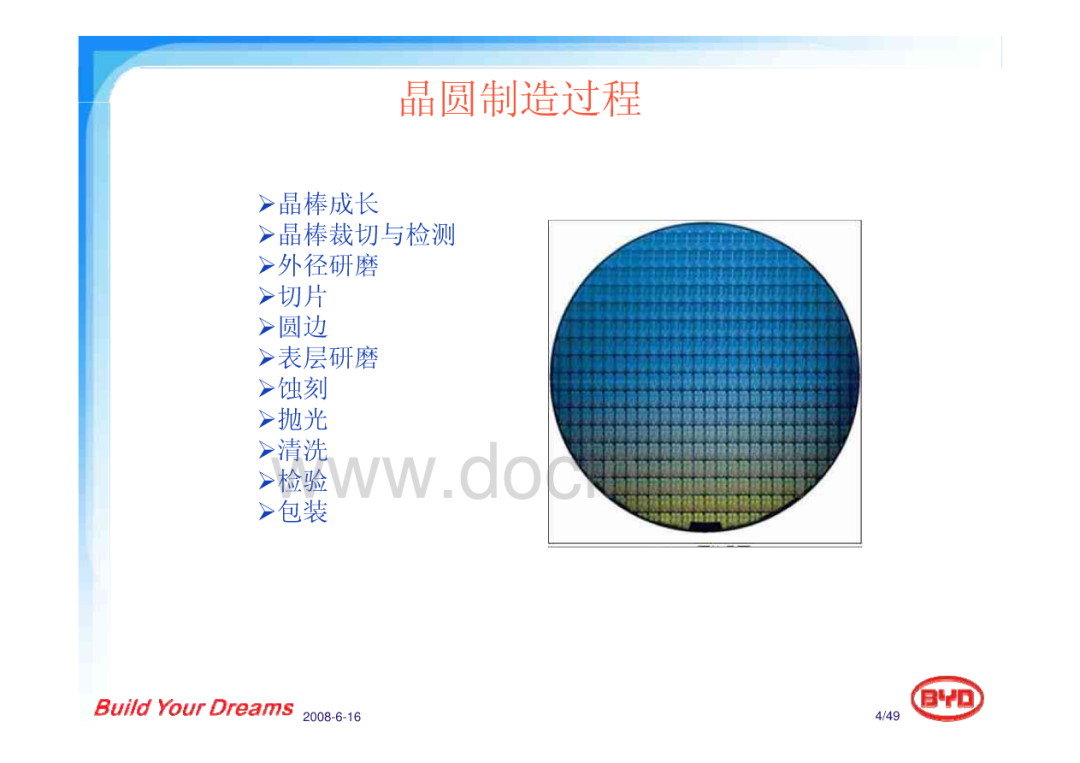

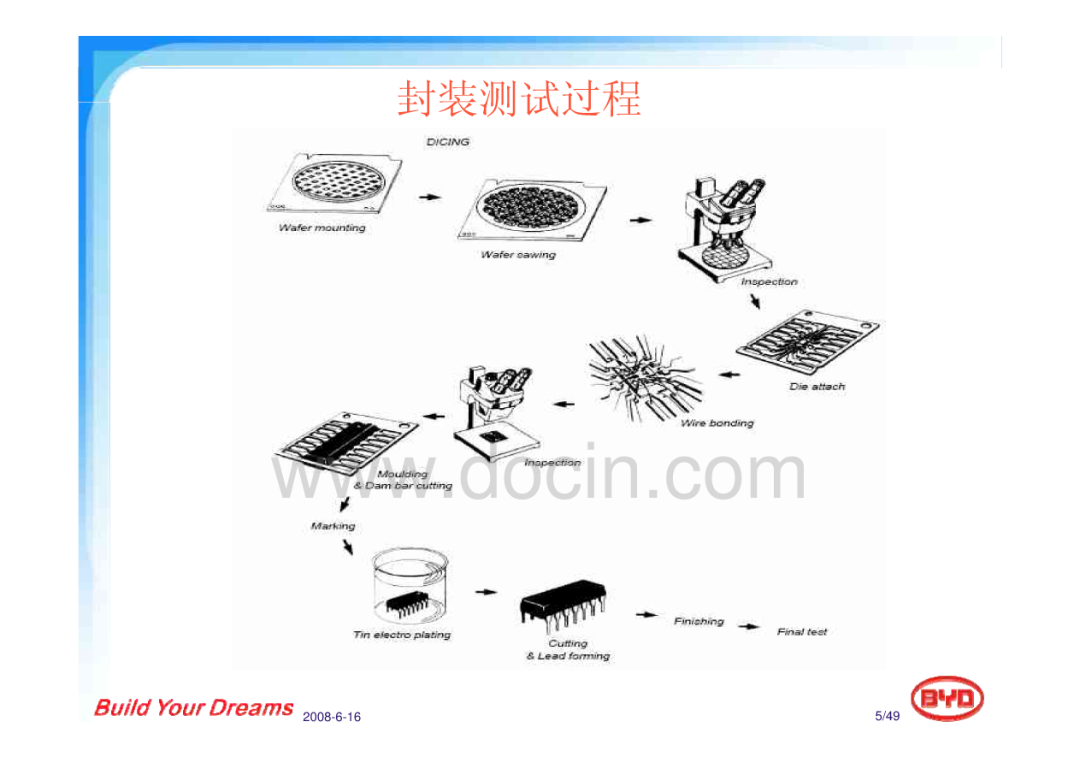

23 2022-05半导体制造工艺

共读好书

本文章来源于网络,仅限于分享交流,如侵权请联络管理人员进行删除. -

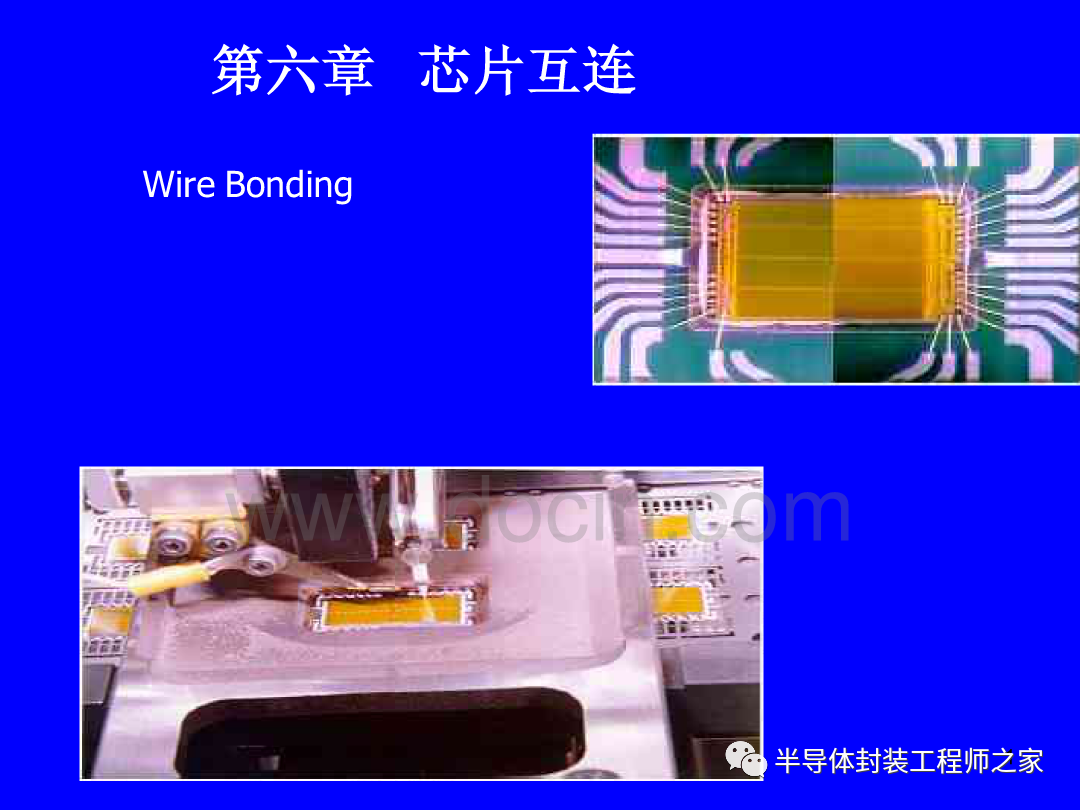

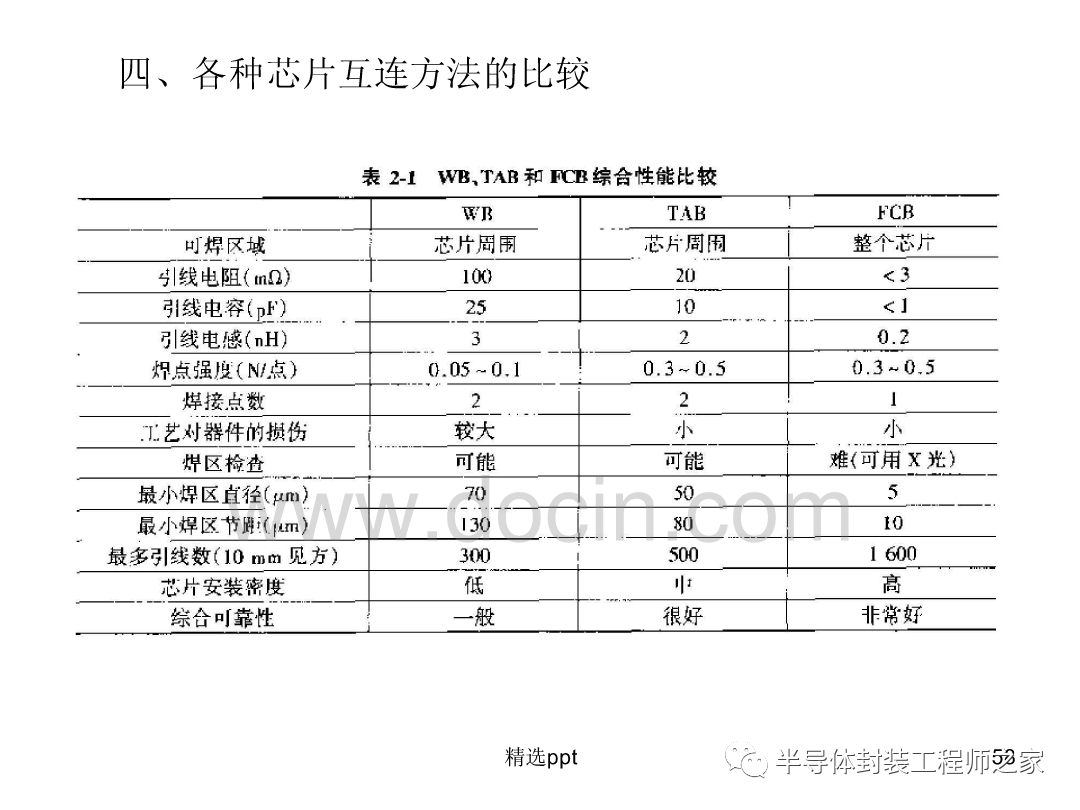

13 2022-05芯片互连

-

09 2022-05什么是晶圆级封装!Die Bond 工艺流程简介

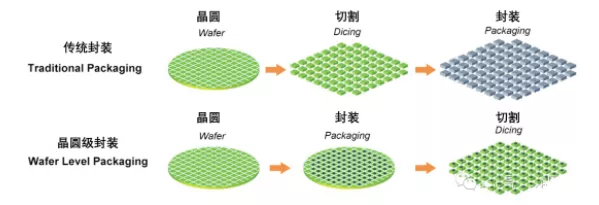

1. 【科普】什么是晶圆级封装!

晶圆级封装(Wafer Level Packaging,缩写WLP)是一种先进的封装技术,因其具有尺寸小、电性能优良、散热好、成本低等优势,近年来发展迅速。根据Verified Market Research 研究数据,晶圆级封装市场 2020 年为 48.4 亿美元,预计到 2028 年将达到 228.3 亿美元,从 2021 年到 2028 年的复合年增长率为 21.4%。

一、晶圆级封装VS传统封装 在传统晶圆封装中,是将成品晶圆切割成单个芯片,然后再进行黏合封装。不同于传统封装工艺,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

相比于传统封装,晶圆级封装具有以下优点:

1、封装尺寸小

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

2、高传输速度

与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。

3、高密度连接

WLP可运用数组式连接,芯片和电路板之间连接不限制于芯片四周,提高单位面积的连接密度。

4、生产周期短

WLP从芯片制造到、封装到成品的整个过程中,中间环节大大减少,生产效率高,周期缩短很多。

5、工艺成本低

WLP是在硅片层面上完成封装测试的,以批量化的生产方式达到成本最小化的目标。WLP的成本取决于每个硅片上合格芯片的数量,芯片设计尺寸减小和硅片尺寸增大的发展趋势使得单个器件封装的成本相应地减少。WLP可充分利用晶圆制造设备,生产设施费用低。

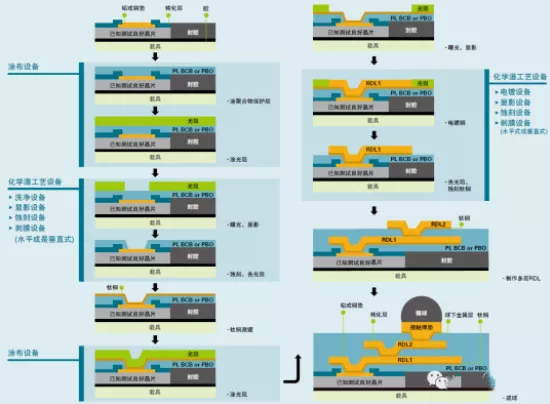

二、晶圆级封装的工艺流程

图 WLP工艺流程

晶圆级封装工艺流程如图所示:

1、涂覆第一层聚合物薄膜,以加强芯片的钝化层,起到应力缓冲的作用。聚合物种类有光敏聚酰亚胺(PI)、苯并环丁烯(BCB)、聚苯并恶唑(PBO)。

2、重布线层(RDL)是对芯片的铝/铜焊区位置重新布局,使新焊区满足对焊料球最小间距的要求,并使新焊区按照阵列排布。光刻胶作为选择性电镀的模板以规划RDL的线路图形,最后湿法蚀刻去除光刻胶和溅射层。

3、涂覆第二层聚合物薄膜,是圆片表面平坦化并保护RDL层。在第二层聚合物薄膜光刻出新焊区位置。

4、凸点下金属层(UBM)采用和RDL一样的工艺流程制作。

5、植球。焊膏和焊料球通过掩膜板进行准确定位,将焊料球放置于UBM上,放入回流炉中,焊料经回流融化与UBM形成良好的浸润结合,达到良好的焊接效果。

三、晶圆级封装的发展趋势 随着电子产品不断升级换代,智能手机、5G、AI等新兴市场对封装技术提出了更高要求,使得封装技术朝着高度集成、三维、超细节距互连等方向发展。晶圆级封装技术可以减小芯片尺寸、布线长度、焊球间距等,因此可以提高集成电路的集成度、处理器的速度等,降低功耗,提高可靠性,顺应了电子产品日益轻薄短小、低成本的发展要需求。

晶圆级封装技术要不断降低成本,提高可靠性水平,扩大在大型IC方面的应用:

1、通过减少WLP的层数降低工艺成本,缩短工艺时间,主要是针对I/O少、芯片尺寸小的产品。

2、通过新材料应用提高WLP的性能和可靠度。主要针对I/O多、芯片尺寸大的产品。

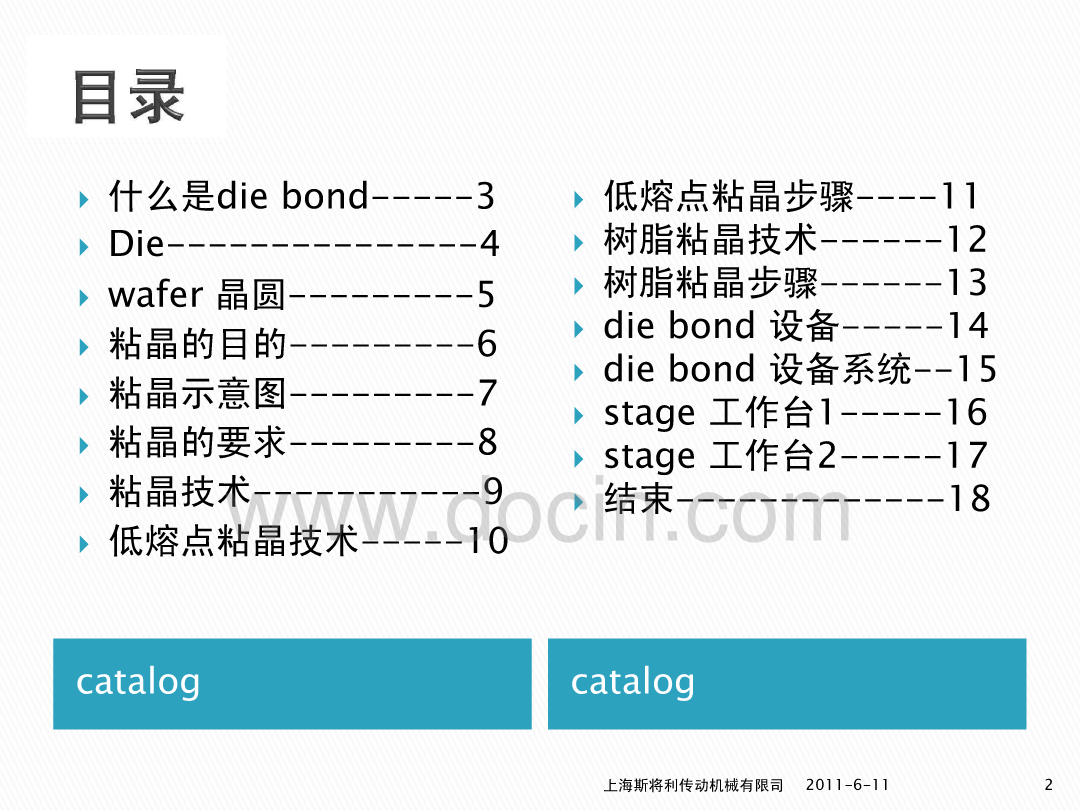

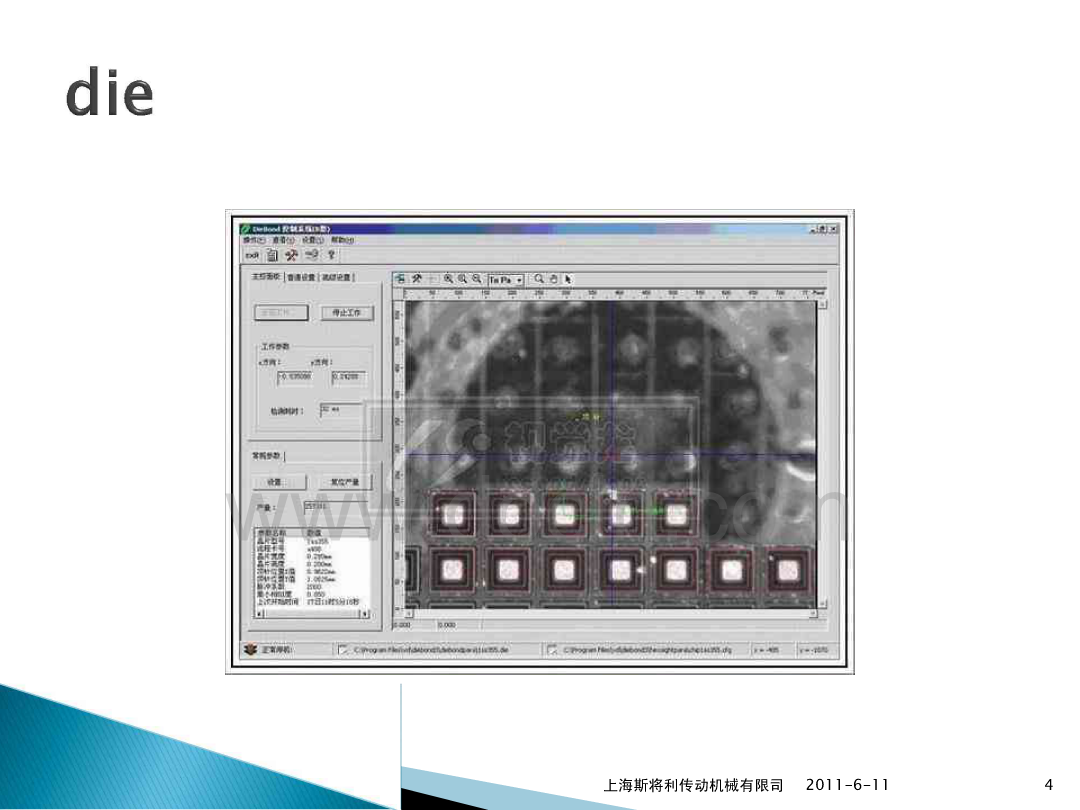

2. Die Bond 工艺流程简介

本文章来源于网络,仅限于分享交流,如侵权请联络管理人员进行删除。